(题图via AnandTech)

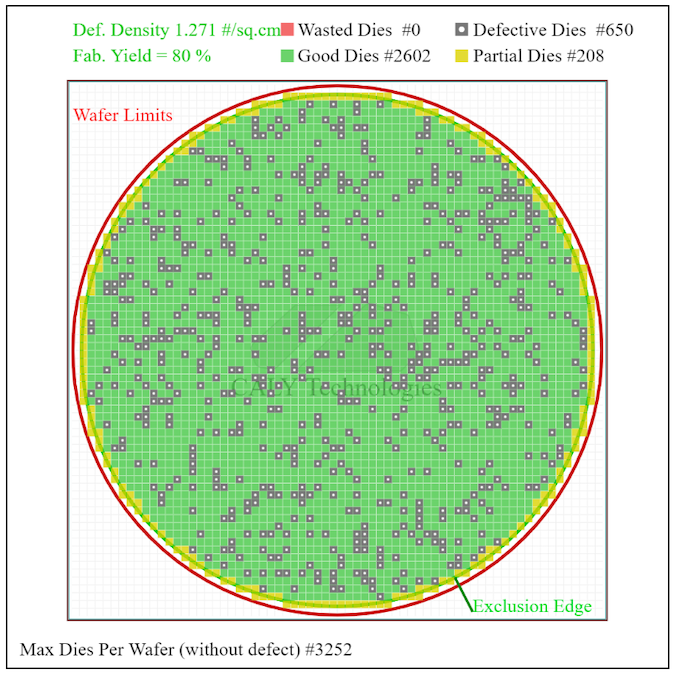

TSMC表示,其5nm EUV可将密度提升约1.84倍、能效提升15%(功耗降低30%)。当前测试的芯片有256 Mb SRAM和一些逻辑器件,平均良率为80%、峰值为90%。

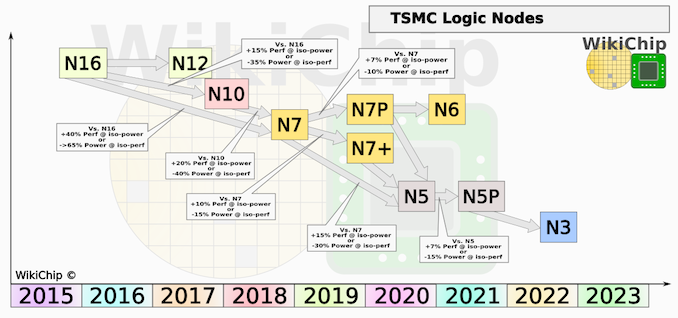

显然,尽管新工艺能够缩小现代移动芯片的大小,但收益率要低得多。目前新技术正在处于早期测试阶段,预计可在2020上半年转入量产,预计5nm成品芯片可在2020下半年准备就绪。

目前TSMC 7 nm工艺可在每平方面积上堆积1亿个晶体管(约96.27 mTr/mm2),5nm新工艺可达177.14 mTr/mm2

作为试产的一部分,TSMC会制造大量的测试芯片,以验证新工艺是否如预期般推进。其中包括一种静态随机存储(SRAM),以及一种SRAM+逻辑I/O芯片。

TSMC展示了具有大电流(HC)和高密度(HD)特性的SRAM单元,尺寸分别为25000/21000平方纳米。同时,该公司正在积极推广有史以来最小的HD SRAM。

至于组合芯片,TSMC表示其包含了30%SRAM、60%逻辑(CPU/GPU)、以及10%的IO组件。SRAM部分为256 Mb,所占面积为5.376平方毫米。

不过TSMC指出,该芯片不包含自修复电路,意味着我们无需添加额外的晶体管,即可实现这一功能。若SRAM占芯片的30%,则整个芯片面积为17.92平方毫米左右。

目前TSMC公布的平均良率约为80%,单片晶圆的峰值良率则高于90%。但17.92平方毫米的面积,意味着它并非高性能的现代工艺芯片。

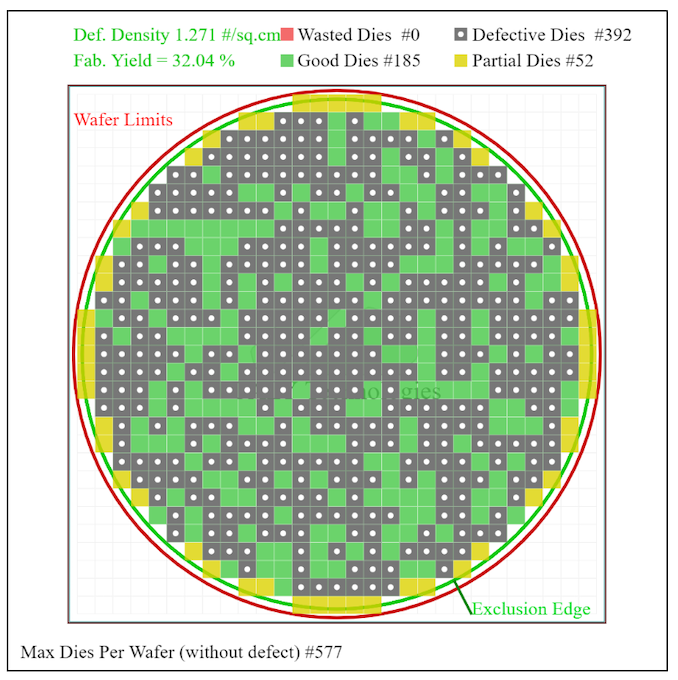

通常情况下,芯片制造商会首先咋移动处理器上小试牛刀,以分摊新工艺的高昂成本吗,比如基于7nm EUV的麒麟990 5G SoC(面积接近110平方毫米)。

尽管AMD Zen 2芯片看起来很大,但并非所有组件都采用EUV工艺生产。不过展望未来,它也更适合迁移至5nm EUV。

在台积电试产的CPU和GPU芯片中,眼尖的网友,应该可以看出一些端倪,比如通过芯片可以达成的频率来逆推良率。

在TSMC公布的数据中,CPU可在0.7 V电压下实现1.5GHz主频,并在1.2 V电压下达成3.25 GHz频率。

至于GPU,图中显示可在0.65 V时实现0.66 GHz频率,并在1.2V电压下提升至1.43 GHz。

对于未来的芯片来说,支持多种通信技术,也是一项重要的能力。因此在测试芯片中,TSMC还介绍了高速PAM-4收发器。

此前,我们已在其它地方见到过112 Gb/s的收发器。而TSMC能够以0.76 pJ/bit的能源效率,达成同样是速率。

若进一步推动带宽,TSMC还可在肉眼可见的公差范围内取得130 Gb/s的成绩,且此时能效为0.96 pJ/bit。(对PCIe 6.0等新技术来说是好事)

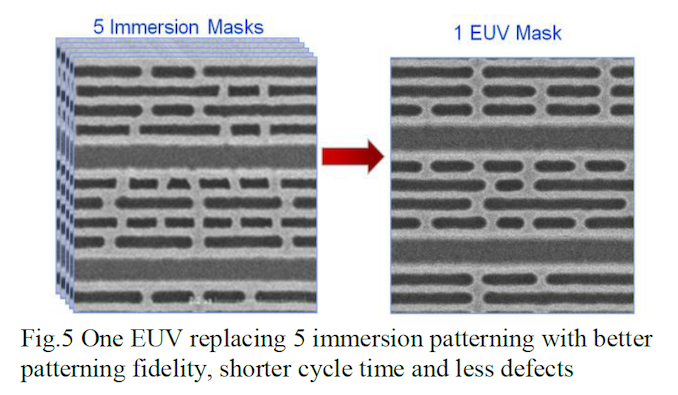

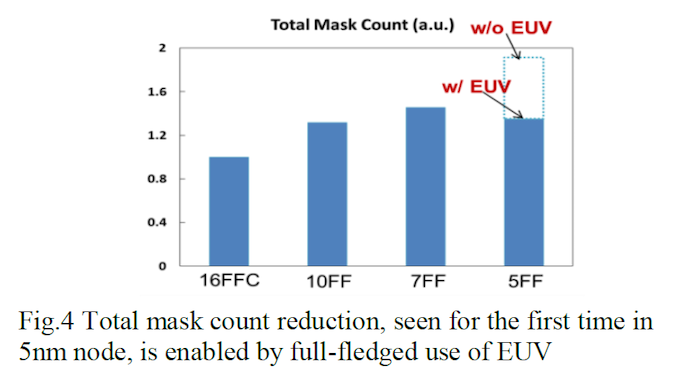

为了改进越来越复杂的EUV工艺,TSMC在基于193 nm的ArF浸没式光刻技术上花费了很多心思。曾经28nm制程的30~40道掩膜,现已在14/10nm上增加到了70道。

有报道称,一些领先的工艺,甚至超过了100道掩膜。好消息是,TSMC在文中表示,其将在10曾以上的设计中广泛使用精简掩膜的新技术。

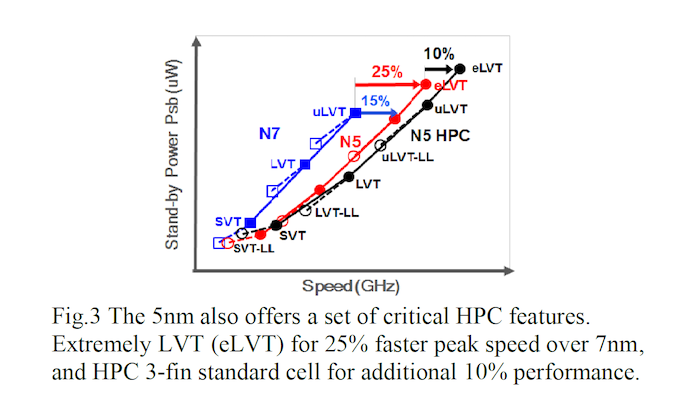

在IEDM上,TSMC还描述了七种不同的晶体管供客户挑选,包括高端的eVT和低端的SVT-LL,uLVT、LVT和SVT(这三种都是低泄漏/LL的衍生版本),以及从uLVT大幅跳跃到的eLVT。