如果三星(Samsung)最近的一支智慧型手机电视广告(大肆吹捧该新手机超酷炫的拍照功能,最后还用‘It'sNotaPhone,It'saGalaxy’的宣传标语作为结束)带有任何暗示意味,那么当今智慧型手机中最重要成份并不是手机,而是相机。

随着相机功能成为差异化嵌入式装置不可或缺的必备功能后,CMOS影像感测器(CIS)的设计人员发现自己正面临与各方需求日益增加的角力战——包括影像品质、相机模组的大小,以及总成本等。

过去几年来,CIS供应商已经逐渐接受晶片堆叠了。在此基础下,CIS能够和影像讯号处理器(ISP)共同堆叠。针对其下一步的发展,目前至少有两家主要的业者——Sony和三星——据称正琢磨使用FD-SOI晶圆制造ISP,以便与CIS共同实现晶片堆叠。

在日前于东京举行的FD-SOI论坛(FD-SOIForum),一些与会者私底下讨论以FD-SOI量产CIS的机会。

除了Sony以外,三星正谨慎地思考为CIS利用FD-SOI。三星电子(SamsungElectronics)系统代工厂总监YongjooJeon在论坛上介绍三星28nmFD-SOI的最新进展时,讨论到CIS等现有应用。

不过,在为CIS导入FD-SOI之前,还有一些重要的问题必须先加以解答。

1、对于可能选用FD-SOI于其晶片堆叠CIS的影像感测器供应商来说,这一CIS市场究竟有多大?

2、晶片堆叠CIS的真正优势何在?

3、在为晶片堆叠CIS设计ISP时,为什么采用FD-SOI比CMOS更好?

CMOS影像感测器市场

根据市场研究公司YoleDeveloppement表示,CIS在2015年约有100亿美元的市场,年成长率约12%。

Yole强调,“CIS的市场成长速度仍然较半导体产业更快,未来五年的复合年成长率(CAGR)预计约有10.6%。”这一预测数字已经将智慧型手机成长放缓以及前/后置相机价格提高等因素纳入考虑了。

那么,哪些CIS供应商已经在做晶片堆叠CIS了呢?

Yole估计在2015年,27%的CIS营收来自于堆叠晶片,该公司形容这“相当于Sony的市占率”。

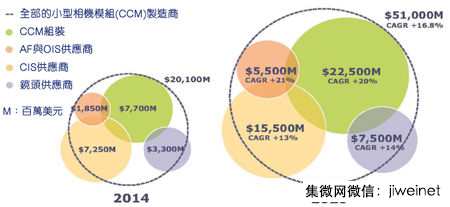

成长中的2014-2020年相机模组产业:营收来源多方重叠

(来源:YoleDevelopment)

为什么采取晶片堆叠途径?

YoleDeveloppement成像与感测器市场分析师PierreCambou观察目前CIS领域的竞争围绕着两大关键参数:影像品质,以及相机模组的尺寸。

他将高品质的相机形容为“智慧型手机的关键要素”。而这也带来了画素的竞赛,从3百万画素(3Mp)到5Mp,然后是8Mp、12Mp、16Mp,如今已经发展到20Mp。

虽然这种发展似乎违反直觉想法,但Cambou表示,这一产业最近已经观察到“画素大小降低了影像品质”。事实上,较高的解析度并不一定会带来“更好的”影像,主要原因在于镜头性能的限制,他解释说。

他补充说:“目前的理想位置大约是略高于1微米画素尺寸,以及介于12Mp到16Mp之间的解析度。”

而在影像品质/画素竞赛的另一面则是相机的成本和尺寸,Cambou解释。更重要的是注意相机模组的尺寸与高度是相当受限的。

“因为智慧型手机是一种高度最佳化的装置,任何可用的空间都会被用于电池或整合进更棒的功能,”Cambou说,“相机的厚度直接影响到智慧型手机的厚度,”以及该装置的外观。

根据Yole的观察,整合于手机中的相机模组一直维持着相当固定的尺寸规格,通常是10mmx10mmx6mm。不过,其性能与功能则持续显着提升(从VGA单镜头到16MpAF以及OIS6镜头相机)。

因此,Cambou表示,堆叠CIS能够解决CIS设计人员的2大关键问题——影像品质和相机的尺寸。

首先,堆叠的方式让晶片设计者能使CIS制程发展仅专注于画素性能,“而不至于对晶片的数位部份造成限制,甚至导致次级晶片性能退化,”Cambou解释。在顶部的感测晶片采用背面照度(BSI)技术。BSI已经是现有可用的最佳技术了,他说,“它可采用相对粗糙的制程,如0.18um至0.110um”。数位晶片可取自任何采用65nm或45nm先进制程的供应商来源。他总结道,“晶片的整体性能可以从最佳化的感测阵列以及最佳化的数位元件中获益。”

其次,Cambou解释,藉由在数位晶片的顶部堆叠感测阵列,还可使其占位空间一分为二,从而实现更小型的相机模组。

手机相机模组市场趋势:供应商多半采用10mmx10mmx5mm的模组

(来源:YoleDevelopment)

晶片堆叠的挑战

当然,晶片堆叠途径也有其挑战性。主要的问题是必须“在一个合理的水平上保有良率”,Yole分析师说:“晶片的成本在堆叠过程中提高了一倍。因此,在设计和制造过程都必须极其稳健。”

Cambou指出,“到现在为止,只有Sony一家公司掌握了这项[晶片堆叠]技术,”尽管三星和Omnivision等公司也发布了堆叠晶片的版本,但一直未能扩大其规模。

他解释说,纯粹以经济问题来看,如果该晶片的数位面积等于感测阵列的面积,堆叠过程将会更有趣。

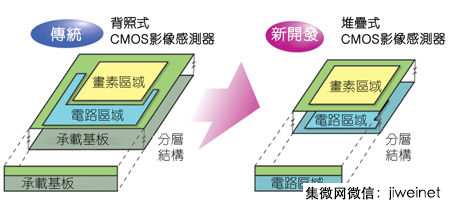

传统背照式与新开发堆叠式CIS的比较

为什么FD-SOI更适用?

Yole分析师认为,FD-SOI为CIS设计者提供了一个“非常有趣的选项”,因为“它能够让‘ISP’次级晶片所产生的热降至最低。”

散热问题至关重要——尤其是对于堆叠于其顶部的感测阵列而言。Cambou解释,“这种热可能会妨碍直接在数位晶片上所进行的大量运算。”然而,Cambou补充说,透过FD-SOI,则为“在APU的ISP中所进行的运算直接整合于堆叠的数位晶片中”开启了可能性。

此外,根据一位日本产业界人士透露,他猜测Sony也很可能正推动在CMOS影像感测器方面的FD-SOI计划进展。

一部份原因在于Sony本身就熟悉SOI晶圆,并深入探讨如何利用SOI晶圆实现基于BSI结构的感测晶片。再者,Sony也持续致力于为堆叠感测器直接接合互连技术。

去年,Sony与制造与ZiptronixInc.共同签署了一项专利授权协议,计划将直接接合互连(DBI)技术应用在影像感测器中。Ziptronix是一家专为3D整合提供低温DBI技术的开发商与供应商。

Sony在2011年授权ZiBond直接接合专利。Ziptronix解释,DBI是ZiptronixZiBond技术的进一步延伸,可实现小于10微米的互连间距,并容纳每平方公分约150万的互连连接。该制程使用标准的晶圆厂工具实现晶圆表面平面化,并导入氧化矽薄层,从而在低温下实现密封接合。

Cambou认为,FD-SOI可望为下一代CIS开启更多新的可能性。采用FD-SOI的可能应用主要包括:

·运算摄影—其中的2个或更多镜头可创造更高解析/灵敏/高动态范围(HDR)的影像

·3D立体成像—类似于运算摄影,实现可能用于手势辨识等其它用途的深度影像

·生物相机—搭配整合的脸部与/和虹膜辨识

·智慧相机—可辨识更多物件

FD-SOI的另一项挑战在于每平方毫米所增加的成本,为良率议题带来了更多压力。不过,Cambou强调,“它或许可为Sony带来加深其与竞争对手差距的大好机会!” 编译:SusanHong