全球物联网、大数据中心、智能家居、便携设备等应用的发展不断丰富着我们的物质生活和精神生活,这些应用的正常运行都离不开半导体数据存储芯片——仅一片指甲盖面积大小的芯片区域就可以存放约300套《大英百科全书》文字内容的高科技产品。近年来,人类社会的数据量迅速激增,一年产生的数据就相当于人类进入现代化以前所有历史的总和,这对存储器芯片的容量和存储密度提出了更高要求。

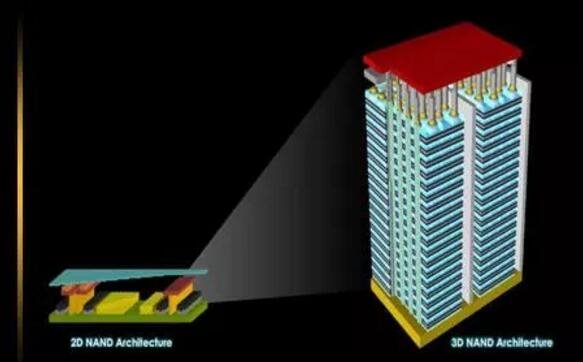

传统半导体存储器芯片通过提高单位面积的存储能力实现容量增长,但在后摩尔时代已不可避免地面临单元间串扰加剧和单字位成本增加等瓶颈。因此,寻求存储技术阶跃性的突破和创新,是发展下一代存储器的主流思路。3D NAND是革新性的半导体存储技术,通过增加存储叠层而非缩小器件二维尺寸实现存储密度增长,将半导体存储器的发展空间带入第三维度,成为未来实现存储器芯片容量可持续增长的关键。

中国作为全球制造业基地,存储器消耗量惊人。据统计,中国存储器消耗量占全球总消耗量的50%以上,但国产存储产品却屈指可数。我国在存储器芯片领域长期面临市场需求大而自主知识产权和关键技术缺乏的困境,开展大容量存储技术的研究和相关产品研制迫在眉睫。2014年6月,国务院印发《国家集成电路产业发展推进纲要》,将半导体产业新技术研发提升至国家战略高度。在此背景下,为推动自主存储芯片技术和产业的发展,中国科学院微电子研究所与长江存储科技有限责任公司建立战略合作,集中开展3D NAND领域关键技术的全方位攻关。

▲常规2D NAND与新兴3D NAND空间结构对比图,图片源自网络

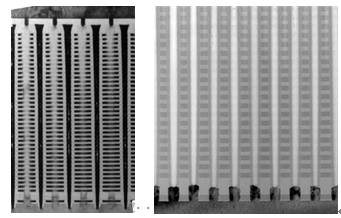

3DNAND芯片的物理结构非常复杂,如果说传统芯片的工艺制作过程如同在硅基材料的微观世界里盖平房,那么3D NAND多层堆叠结构的实现则是筑起高楼大厦的高难度工程,这给半导体工艺制造带来了全新挑战,需要在工艺流程上解决高深宽比刻蚀、高选择比刻蚀、叠层薄膜沉积、存储层形成、金属栅形成以及双曝光金属线等关键技术,才能实现特性稳定、良率较高的存储核心结构。

▲3DNAND多层堆叠结构TEM照片,图片源自长江存储

存储器的可靠性是影响产品品质的重要一环,数据耐久性、数据保持特性、耦合和扰动是可靠性的主要评估特性,综合反映了存储器可以正确存取资料的使用寿命。NAND型存储器的普遍寿命在10年左右。由于不可能在自然条件下进行测试,研发人员采用存储器加速老化的测试方法,在1-2周内模拟数十年的过程,通过大量实验数据的组合分析,寻找影响可靠性特性的关键因素。同时,研发人员还建立了三维存储结构的理论及工程模型,并应用创新性的电路设计技术,保证芯片各项指标达到产品级别。

目前,由微电子所与长江存储联合开展的3DNAND关键技术攻关已取得重要进展,研发的32层存储器芯片顺利通过电学特性等各项指标测试,达到了预期要求,系国内首次实现3D NAND工艺器件和电路设计等一整套技术验证,标志着我国3D NAND存储器研发向产业化道路迈出了关键一步。