最近,关于iPhone6sA9处理器版本的事情的话题很热,最后都闹到苹果不得不出来解释的地步,先不评判苹果一再强调的整机综合续航差2~3%的准确性,但是三星14nm工艺相比台积电16nm工艺较差已经可以说是板上钉钉的事了。

那么问题来了,工艺不是纳米数越小就越好吗?14nm怎么会比16nm还差呢?这个问题不仅小白消费者困惑了,连看似专业的Anandtech和GeekBench的人也表示不解。其实对这个结果,真正半导体领域特别是工艺领域的从业人员是有预期的,其中的原因也是非常清楚的,既然大家有这么多困惑,我就尽量用通俗易懂的方式解释给大家听听。

要解释清楚台积电16nm好于三星14nm这个问题,首先要回答下面几个问题:

1、为什么工艺越先进(纳米数越低),功耗和性能都会提升?

2、在每个工艺节点(纳米数相当)上,是否也同样存在不同的功耗和性能的工艺选择?

3、Finfet又是什么?

4、台积电和三星都在具体的工艺实现上做了哪些选择,最终导致台积电16FF+相比三星14LPE更优

为什么工艺越先进(纳米数越低),功耗水平和性能都会改善?

这要从晶体管说起了:

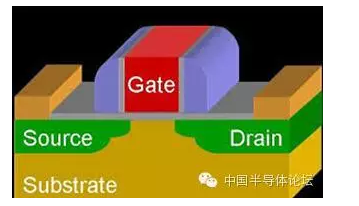

关于半导体基础知识,外面的专业文章一搜一大把,但是都不是给正常人看的,所以我就把那些曲线和拗口的各种材料名扔一边,让事情简单一点,用个最简单的模型给大家讲解。上面这副示意图中就是一个典型的半导体晶体管。其中两个绿色的部分分别是晶体管的两级,类似电池的两级。红色的部分就是用来控制这两个电极的通断的,而通断分别对应数字化时间的1和0,所以所谓数字化世界其实也就是非常非常非常多的晶体管的通断变化组合出来的。红色Gate的宽度就是我们通常所说的沟槽宽度或者线宽,我们通常说的多少多少nm就是指的这个宽度。大家注意这可是纳米,1000纳米=1微米,1000微米=1毫米,大家这下有概念了吧。

那么这个Gate的宽窄为什么会影响性能和功耗呢?先说性能,性能好意味着在一定的时间干更多的事,在处理器里就是更多的运算,我们可以当半导体晶体管每次0/1变化就算一次运算,那么那个红色Gate越宽,两个绿色电极就越远,导致他们直接连通一次的时间就会越长。这就好比一个人在10分钟里做25m往返跑的次数肯定比50m往返跑的次数多一样。所以Gate越小,晶体管一次状态变化的所需时间就会越短,单位时间的工作次数就会越多,一堆晶体管单位时间可做的运算自然就更多,所以性能更好。

再说说功耗。Gate是通过加电压帮助两个绿色电极通电的,而Gate越宽,就需要更高的电压才能导通两极,Gate越窄,导通就更容易,所需的电压也就越低。这很容易理解,离得近容易通,离得远不容易通,要通就需要使更大的力气。那么学过基础电学知识的都知道功耗的大小与电压的平方成正比(如下:)

P(功率)=V2(电压的平方)

R(电阻)

所以导通电压的下降是新工艺能够降低功耗的主要因素。还有一个因素,即便是电压相同,通过导体的面积和长度越小,电流也会越小。更小的Gate等于是缩小的导体,因此也会减少功耗。

就是这些原因带来了先进工艺(更窄的Gate)带来的好处,那么这个好处有多大呢?下面一组数据是几个典型工艺的相应性能、功耗的改进数据,我们看到还是很可观的。这也是半导体厂商追逐工艺的一个重要的原因。

在每个工艺节点(纳米数相当)上,也会有很多不同性能功耗水平的版本

Gate的宽度是工艺特性的一个主要因素,更准确的说是决定了一代工艺的特性范围。由于三星和台积电在技术来源上存在一些不同,我们会看到一些具体数值上的差异,但是同代工艺实际上在总的范围上是类似的。下表是三星和台积电同代工艺的大致对应关系,所以三星的14nm和台积电16nm是同代工艺。

在每代工艺的特性范围内,还有其它很多因素影响着工艺的性能和功耗水平。先说两个数据大家感觉一下,28nm的Wafer(晶圆)生产过程中需要做40多层Mask,而用了FinFet技术的14/16nm,更是需要近60层的Mask。所以大家千万不要以为确定了Gate的宽度,就什么都定了,其实这好几十层的工艺过程中,还是有很多不同的材料和设计可以带来不同的性能功耗差异。

下表是从台积电官网复制下来的一个表格(http://www.tsmc.com/english/dedicatedFoundry/technology/28nm.htm),是台积电的28nm工艺下的不同版本列表,有5个之多,而且特性差距也是很明显的。其中28HPM和28LP是手机芯片的两个常用的工艺。28HPM相比28LP最大不同是在晶体管Gate底部采用了High-K的材料,通过这个可以显著提升性能和功耗。具体什么是High-K我们这里就不展开了,大家只要知道同代工艺的不同版本也会有不同的特性就行。这样便于理解三星14nm和台积电16nm作为同代工艺,但在实际特性上会存在一定的差异。

Finfet又是什么?

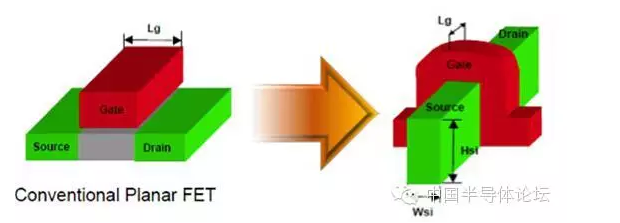

刚才讲到Gate越窄,也就是纳米数越低,功耗和性能的收益都很明显。但是世界上所有事情都有两面,有收益就会有代价。左图中红色Gate越窄,则Gate接触下面的面积就越小,前面说了,绿色SD两极的通断是靠Gate通电压控制的,但是面积越小这个Gate的控制力越弱,这就会导致出现两极之间的漏电越来越大,这个问题在20nm达到了一个很大的值,对功耗影响很大。所以早在10年前,就有人提出了新结构(右图),3D晶体管,由于这个结构看上去像张开的鱼鳍,所以被叫做FinFET技术。FinFET技术最主要的好处是红色的Gate变成三面环绕绿色SD两极之间的通道了,这样Gate就又重新具备了对这个通道的强力控制力,原先通过减小Gate宽度的方法就可以继续了。所以,三星和台积电也都是在其14/16nm的这一代工艺开始用上FinFET技术。有人可能会有疑问,十年前就提出为什么现在才用,其实概念到实施不是那么容易的,大家脑补一下这个结构是在20nm的范围里做的,导致工艺要多出十几二十层来,这不仅是难度,也是成本,所以两家都在这个相似的时间应用到新产品中也侧面说明三星14nm和台积电16nm是同代工艺。

台积电16FF+相比三星14LPE更优的真正原因

上面说了这么多,我无非是想帮大家先搞清楚两个基本概念:

1、别看14nm数字小,三星14nm和台积电16nm是同代工艺;

2、同代工艺不同实现是会带来性能功耗特性的明显差异。

既然大家知道了同代工艺不同实现会带来差异,那我们看看三星14LPE和台积电16FF+在实现上到底有哪些不同,从而带来我们看到的差异。

为讲清楚这件事,请容我简单回顾一下历史。台积电作为芯片代工领域的老大很多年了,不是为别的,主要还是凭其技术能力有领先性,而三星作为后来者也一直在进步,两家的几个主要工艺推出的时间如下表:

从上表我们可以看到,三星在14nm之前,每一代一直是落后台积电1年左右时间的,而之后它跳过了20nm这一代,直接推出14nm的产品,跳到了台积电前头。关于这个事情有很多的传说,有兴趣的可以自行度娘一下“台积电梁孟松”就好。但是我们也都知道,这种大跃进式的发展一定有其弊端,那么三星这次的14nm大跃进也自然会遇到了大问题,这个大问题就是良率。

良率(良品率)是半导体领域的一个关键数据,因为就像从一块大的圆镜子上要切割出完好的小方块镜子一样,切出的小方块镜子完好的越多,则良率越高。影响良率的因素非常多,毕竟一个晶体管就十几二十纳米大,每个芯片都有几十亿个晶体管,随便一点材料污染或者工艺波动都会造成报废。而买一个大圆镜子的成本是固定的,良率越高分摊到每个小镜子的成本就越低。每个工艺开始的阶段,良率都不高,更何况三星跳过20nm这一代,少了很多经验积累,所以良率低得不能看。再加上前面说了,FinFET技术需要多出十几二十层mask,每一层都是要算钱的,所以这两个因素一叠加,那么芯片的成本就会贵的离谱。有多离谱?我只能说比史上最贵的手机SOC-高通810还贵得多。所以你要是三星会怎么办,那当然是想尽办法降成本呗,要不卖不出去啊。所以在工艺的具体实现上,台积电由于对良率有更好的把握,所以可以选择在成本上更宽松的方法,比如增加mask层数,来保证更好的性能和功耗,而三星只能用保成本的方法但是牺牲了功耗。

也许有人会问,既然这样,那苹果、高通都傻啊,为啥要用它的呢。要知道这些数据只有真正出来时才可以证实,早期选工艺的时候只有厂家提供的数据做参考,完全可以想象三星但是拿着多么漂亮的一套PPT去忽悠,时间早东西好,确实诱人啊。不过苹果确实不傻,估计也是将信将疑,所以在台积电又开了一摊,现在还是有退路的,而高通同学的820估计就又坑了。