近日,“英特尔精尖制造日”活动在京举行。英特尔公司执行副总裁,制造、运营与销售集团总裁Stacy Smith否定了业界传出的“摩尔定律失效”的说法,并且首次在中国展示英特尔首款10纳米FPGA的计划,并宣布了业内首款面向数据中心应用的64层3D NAND产品已实现商用并出货。

图:英特尔公司执行副总裁,制造、运营与销售集团总裁Stacy Smith

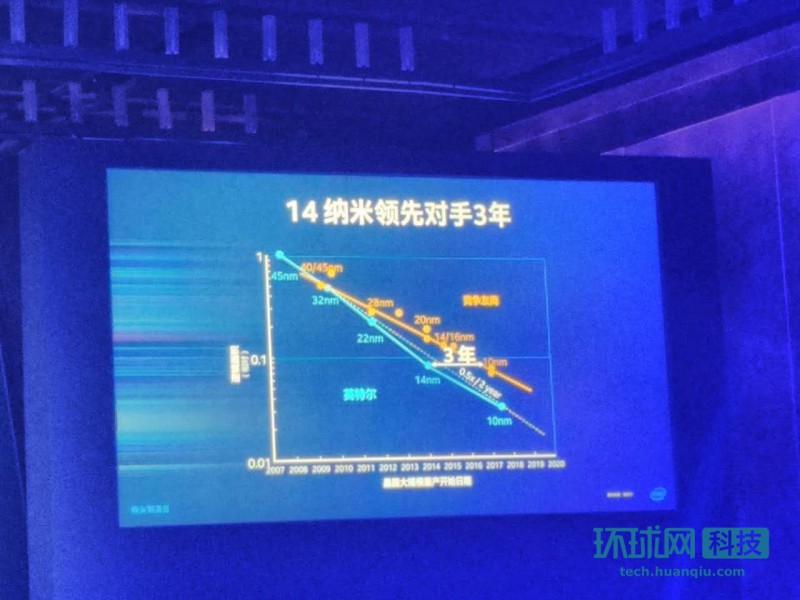

“英特尔一直以来都是,并将继续成为推动摩尔定律向前发展的技术领导者,目前英特尔在制程工艺上保持着大约三年的领先性。”Stacy Smith进表示,英特尔推动摩尔定律不断向前发展,每一年都持续降低产品价格并提升其性能,这也是英特尔的核心竞争优势所在。

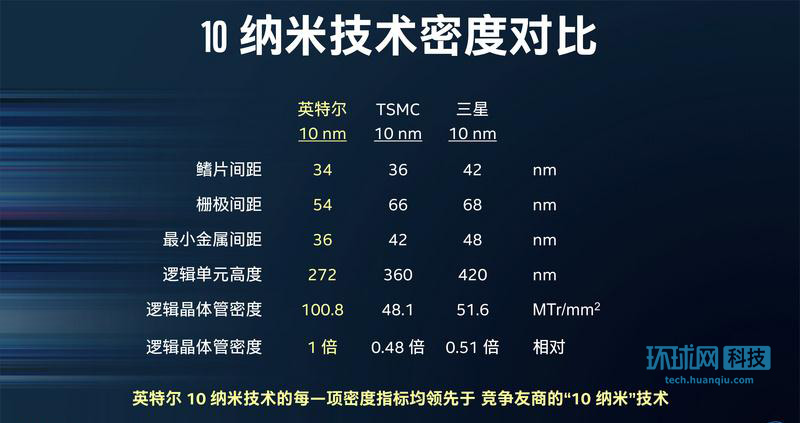

他提到,正是超微缩技术(hyper scaling)让英特尔能够加速推进密度的提升,借助节点内优化,产品功能每年都可以实现增强。据悉,英特尔10纳米制程工艺拥有世界上最密集的晶体管和最小的金属间距,从而实现了业内最高的晶体管密度。

Stacy Smith指出,英特尔10纳米制程的最小栅极间距从70纳米缩小至54纳米,且最小金属间距从52纳米缩小至36纳米。尺寸的缩小使得逻辑晶体管密度可达到每平方毫米1.008亿个晶体管,是之前英特尔14纳米制程的2.7倍,大约是业界其他“10纳米”制程的2倍。

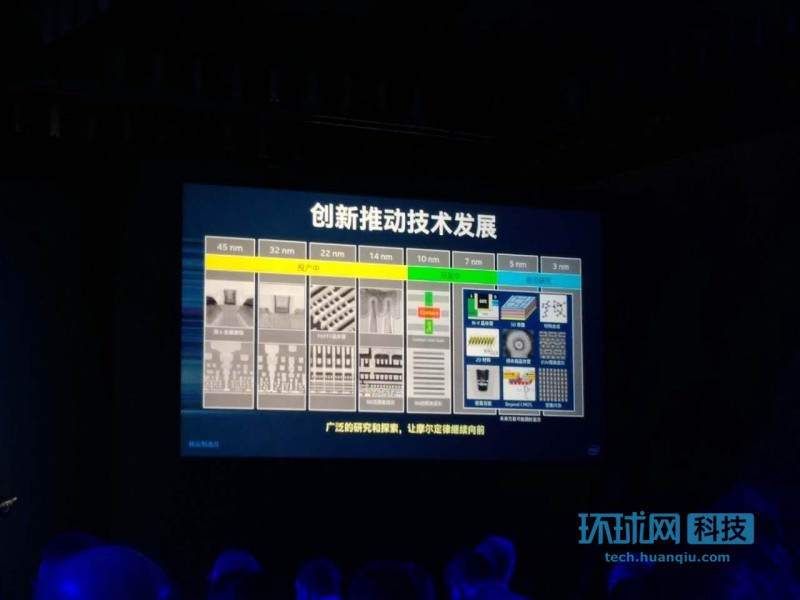

对于业界探讨的“摩尔定律是否失效”的问题,Stacy Smith坚定的认为不会。“每一个节点晶体管数量会增加一倍,14nm和10nm都做到了,而且晶体管成本下降幅度前所未有,这表示摩尔定律仍然有效。”Stacy Smith解释道,“创新技术,可以保证摩尔定律长期有效。”

另外,现场还展出了经过展讯验证的英特尔晶圆代工业务14 纳米平台。英特尔14纳米制程采用第二代FinFET 技术,提升性能并降低漏电功耗。

英特尔高级院士马博(Mark Bohr)介绍了英特尔22FFL功耗和性能的最新细节。22FFL是在2017年3月美国“英特尔精尖制造日”活动上首次宣布的一种面向移动应用的超低功耗FinFET技术。英特尔22FFL可带来一流的CPU性能,实现超过2GHz的主频以及漏电降低100倍以上的超低功耗。此外,22FFL晶圆在本次活动上全球首次公开亮相。

据悉,与先前的22GP(通用)技术相比,全新22FFL技术的漏电量最多可减少100倍。22FFL工艺还可达到与英特尔14纳米晶体管相同的驱动电流,同时实现比业界28纳米/22纳米平面技术更高的面积微缩。22FFL工艺包含一个完整的射频(RF)套件,并结合多种先进的模拟和射频器件来支持高度集成的产品。

2017年6月,高通总裁里克·阿伯利曾表示,之前的处理器龙头Intel在10nm制程技术明显落后;高通方面也曾表示,骁龙835处理器采用的是三星10nm芯片制造技术,这意味着其移动芯片超过了个人计算机处理器。

在业内人士看来,一向低调的英特尔在活动当天不断提到友商的问题;从来不跟友商比较的英特尔还明确地跟三星和TSMC在10纳米技术上做对比。尤其在媒体采访环节,英特尔中国区总裁杨旭提到了制程节点命名的混乱,认为制程技术应该以实践进行度量;在媒体的追问下,他给出强势回应“老虎不说话(发威),当我们病猫呢”。

最后,Stacy Smith认为,“我们在14nm上与竞争对手相比领先3年。可以看到友商晶体管密度并没有提升,友商10nm节点晶体管密度只相当于我们14nmd的晶体管密度。”