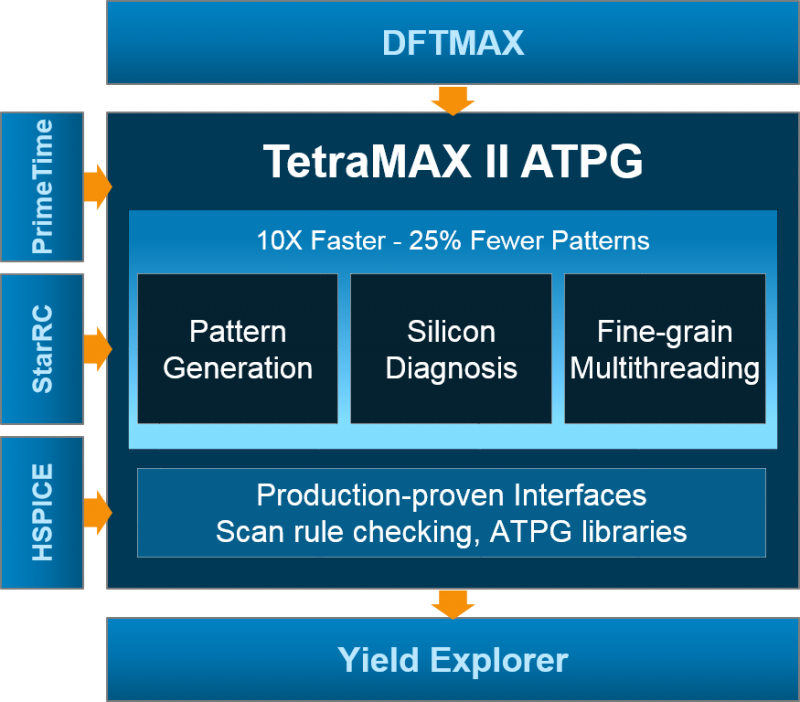

前不久,新思科技揭晓其下一代ATPG和诊断解决方案TetraMAX®II。该方案结合了2015年10月在国际测试大会上发布的创新测试引擎。TetraMAXII能够将运行时的速度提高至少一个数量级,将ATPG运行时从数天缩短到数小时,确保在初步硅晶样品首次用于测试时将向量准备就绪。此外,TetraMAXII生成的向量数量减少25%,使IC设计团队能够缩短测试硅晶部件的时间并减低成本,而且还能应汽车等特殊市场细分的要求,在不影响测试成本的前提下提升测试质量。经过生产验证的ATPG界面的复用可以确保无风险地轻松部署到设计和测试流程中。用户将在班加罗尔里拉皇宫酒店(LeelaPalaceHotel)举办的Synopsys用户集团(SNUG)印度会议上分享其对TetraMAXII的使用体验。

据Synopsys设计集团执行副总裁兼总经理AntunDomic表示:“世界各地的设计人员依靠Synopsys基于综合的测试解决方案来在其最具挑战性的设计上实现最高的测试质量。TetraMAXII证明我们在不断践行承诺,提供创新和突破性测试技术,并且满足客户对于更快ATPG和诊断的需求以及减少硅晶测试时间的需求。”

Synopsys基于综合的测试解决方案包括用于可测试性分析的SpyGlass®DFTADV、以及基于功耗敏感测试与硅片诊断的DFTMAX,DFTMAXUltra、TetraMAXI和TetraMAXII;用于IP和SoC内核分层测试的DesignWare®STARHierarchicalSystem;用于嵌入式测试、修复和诊断的DesignWareSTARMemorySystem®解决方案;用于以设计为中心产量分析的YieldExplorer工具;以及用于CAD导航的Camelot™软件系统。Synopsys的测试解决方案结合了DesignCompiler®RTL综合以及嵌入式测试技术,可优化时序、功率、区域、拥塞,以供测试之用,还可优化功能逻辑,从而在更短时间内获得成果。Synopsys测试解决方案提供跨SynopsysGalaxyDesignPlatform的紧密集成,包括DesignCompiler、ICCompiler™II布局和绕线工具,以及PrimeTime时序验收,以实现更短的周转时间,同时满足设计与测试目标,实现更高的缺陷覆盖以及更快的良率提升。

更为重要的是,SGS-TÜVSaarGmbH是可信任的独立评估方,正式鉴定认可了TetraMAXII,并认可TetraMAXII拥有深度功能安全资格。该认证为使用TetraMAXII进行安全关键型汽车应用设计的设计人员提供了极深的信心,加速了汽车IC的功能安全资格的获得,包括最为严格的汽车安全完整性等级(ASILD)要求。

在交付完全智能驾驶汽车的过程中,汽车制造商正在快速部署先进驾驶辅助系统(ADAS),帮助司机减少事故。由于这些系统中的故障可能导致不可接受的后果,汽车制造商会与其供应商合作提高IC质量、可靠性和功能安全。通过测试多个故障模型,同时尽量减小对测试成本和测试向量生成时间的影响,TetraMAXII支持工程师以更高的IC测试质量为目标,这是汽车产品的关键要求。为了确保使用最佳工程实践尽量减小故障风险,从而避免影响汽车IC的功能安全元素,ISO26262定义了开发过程中使用的软件设计工具的资格要求。SGS-TÜVSaarGmbH鉴定TetraMAXII符合ASILD标准,这是ISO26262规定的最高等级的功能安全标准。

SGS-TÜVSaarGmbH功能安全软件部门产品经理GudrunNeumann说:“符合ISO26262认证资格的工具,可以帮助提高工程师对于EDA软件工具的信心,放心地为电子安全系统开发汽车IC。工具达到ISO26262最严格的ASILD应用要求,IC设计团队就能促进产品符合整体功能安全认证要求。Synopsys的TetraMAXIIATPG符合开发安全相关电子系统所用软件工具的ASILD安全要求。SGS-TÜVSaarGmbH鉴定TetraMAXII是基于其在验证流程的功能安全评估中达到了ISO26262要求。”

Synopsys设计集团营销副总裁BijanKiani说:“世界各地的Synopsys汽车IC客户都相信TetraMAXATPG能让其最复杂的设计实现最佳测试质量和最低测试成本。我们的新TetraMAXIIATPG解决方案支持我们践行承诺,帮助汽车IC设计团队加速制造中的测试开发。它可以将ATPG运行时从数天加快到数小时,并通过将向量数量减少25%来降低测试成本。对于汽车IC应用而言,TetraMAXII提供了机会,可使用多个故障模型提高测试质量,而不对测试成本和测试生成时间造成显著影响。此外,TetraMAXII认证可帮助达到ISO26262标准的功能安全要求。”

凭借TetraMAX®IIATPG,意法半导体极大加快了测试向量生成运行时间,并减少了向量数量。意法半导体面临着其系统级芯片(SoC)复杂性增加和上市时间日程缩短的挑战。为了应对这些挑战,意法半导体需要快速的周转时间来生成高质量的制造测试向量。TetraMAXII使用数百万门FD-SOISoC设计来跟踪评估,在不影响测试覆盖的前提下显示了运行时速度的数量级增长以及测试向量数量的大幅减少。结果,意法半导体正在其标准SoC设计流程中部署TetraMAXII。

意法半导体数字及混合工艺ASIC部SoC集成和DFT方法经理RobertoMattiuzzo表示:“在过去几年中,我们与Synopsys通力合作,共同应对复杂性和制造成本增加以及更优质、更快速周转时间需求等日益增长的制造测试挑战。在我们对高密度FD-SOI芯片评估的过程中,TetraMAXII生产测试向量的速度加快了一个数量级,同时在不造成任何覆盖损失的前提下大幅减少了向量的数量。因此,我们有信心更早地测试第一个硅晶样品,并且缩短测试时间。”

Synopsys设计集团执行副总裁兼总经理AntunDomic表示:“意法半导体等客户依靠Synopsys的测试解决方案来确保快速周转时间、低测试成本和高质量的最佳组合。我们与意法半导体的长期合作不断壮大。凭借其TetraMAXII评估的最新成果,我们再次展示了我们持续提供ATPG和相关技术创新以应对客户制造测试挑战的坚定承诺。”

东芝同样已经确认SynopsysTetraMAX®IIATPG能够极大加快测试向量生成,缩短生产测试时间,并降低成本。由于即将推出的复杂SoC测试质量要求高,设计进度要求紧迫,东芝设计人员决定他们需要一种更快速的ATPG解决方案,以便在确保充分功率感知的同时,大量减少生成的测试向量。为了满足这些需要,并且随后全面评估的结果显示向量数量减少达50%,运行速度显著加快,并拥有先进的功率感知功能,东芝计划为其最新的消费电子SoC设计部署TetraMAXII。东芝将于7月13日在班加罗尔里拉皇宫大酒店(LeelaPalaceHotel)召开的Synopsys用户群(SNUG)印度用户大会上分享其使用TetraMaxII的经验。

东芝设计技术开发部高级经理KazunariHorikawa表示:“较长的ATPG运行时间以及日益增长的测试向量数量正在为我们的大规模SoC设计带来越来越大的挑战。在保持测试质量的同时实现测试成本最小化,这需要减少测试向量并缩短运行时间。我们一直在与Synopsys合作,并且通过评估确认:TetraMaxII在保持测试质量的同时,能够缩短ATPG执行时间,并将测试向量的数量减少高达50%。我们计划在在即将推出的SoC设计上采用TetraMAXII,并且相信TetraMAXII将凭借其强大的路线图,进一步降低测试成本。”

Synopsys设计群组执行副总兼总经理AntunDomic表示:“Synopsys致力于满足世界各地设计人员不断发展的测试需求。我们与东芝近期的合作展示了我们对新型测试技术的持续创新和投入,这使我们能够在设计复杂性不断增长之时,满足客户对于缩短生产测试时间和加快ATPG的需求。”

整体而言,TetraMAXII在新的测试向量生成、故障模拟和诊断引擎上构建,这些引擎十分快速、极为节省内存,并经过高度优化,适合生成向量和执行精细化多线程的ATPG和诊断流程。这些创新导致了测试向量的显著减少,并将ATPG时间从数天减少到数小时。TetraMAXII的内存效率允许利用所有服务器内核,而不计设计尺寸,因而胜过了之前受限于高内存使用率的解决方案。经过生产验证的设计建模与规则检查架构的复用以及用户和工具界面可确保设计人员能快速、无风险地在极具挑战性的设计上部署TetraMAXII。此外,TetraMAXII还利用与GalaxyDesignPlatform工具建立的链接提供最高质量的测试和最快速、生产力最高的流程,这些工具有DFTMAX™压缩、PrimeTime®时序分析和StarRC™提取,还有包括YieldExplorer®以设计为中心的产量分析和Verdi®调试工具在内的其他Synopsys工具。