三星(Samsung)即将量产用于其Exynos8SoC的14奈米(nm)LowPowerPlus(LPP)制程,这项消息持续引发一些产业媒体的关注。三星第二代14nmLPP制程为目前用于其Exynos7SoC与苹果(Apple)A9SoC的第一代14nmLowPowerEarly(LPE)制程提供了进一步的更新。

业界目前共有三座代工厂有能力制造这种鳍式场效电晶体(FinFET):英特尔(Intel)、三星和台积电(TSMC)。TechInsights曾经在去年五月剖析用于Exynos7420SoC的三星14nmLPE制程,当时在讨论这项用于制造电晶体的制程技术时仍有所限制。而今,在几乎过了一年后,大家已经开始讨论三星的升级版14nmLPPFinFET制程了。

然而,预计要到今年春季末取得三星的Exynos8890SoC或高通(Qualcomm)的Snapdragon820SoC样本后,才可能完全掌握这项制程技术的细节。不过,我们可以进一步揭密用于Exynos7420SoC的更多14nmLPE制程技术细节,同时也有助于预期下一代LPP制程的新进展。

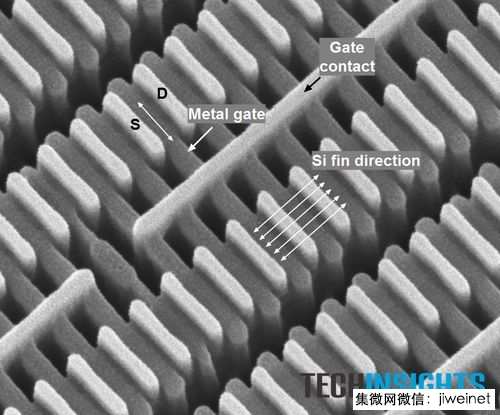

我们从观察典型三星14nmLPEFinFET电晶体的SEM侧视图开始(图1)。电晶体通道如同矽鳍片(SiFin)般地形成,而非由图片的左下角向右上方生长。这些鳍片被埋在电介质下方而无法直接看到,因此,我们以箭号指示其方向。金属闸就位于正交方向,覆盖在整个鳍片的两侧与顶部。在闸电极的任一侧可看到较大的源极与汲极(S/D)触点。

图1:三星14nmLPEFinFET电晶体的侧视SEM图

(来源:TechInsights)

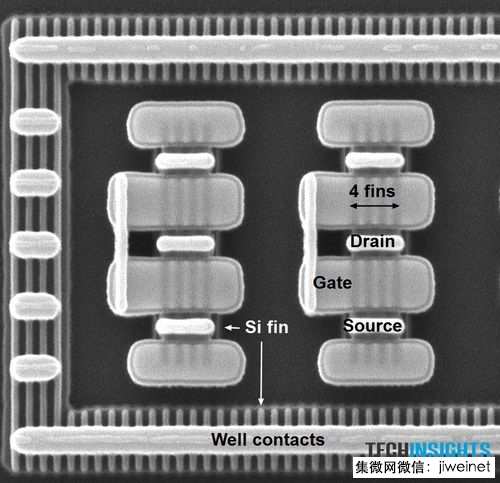

也许从另一张三星FinFET电晶体的平面图(图2)中能更清楚的看到闸极与鳍片的布局。四片矽鳍以垂直的方向排列在水平方向的金属闸极正下方。这两种电晶体结构周围都围绕着一个阱触环,用于隔离其与晶片上的其他电路部份。

该鳍片间距约有49nm,必须采用双重图案制程来制造。在此提供了两种选择:英特尔所使用的‘双微影蚀刻’(LELE),或是‘自对准双微影图案法’(SADP)。我们认为三星采用了LELE制程为鳍片制图,但最后还需要额外使用光罩与微影制程,才能中断电晶体的两端。

图2:三星14nmFinFET电晶体的平面图

(来源:TechInsights)

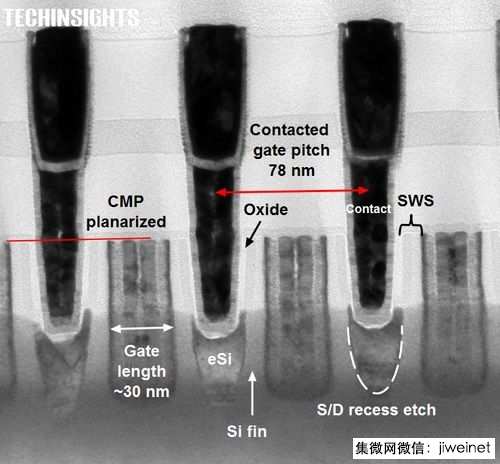

图3是Exynos7420所使用的典型NMOS电晶体之TEM横截面图,而且我们还注意到闸极长度经测量约有30nm,这跟所宣称的14nm制程节点差距颇多,而在表1中所整理的英特尔和台积电的情况也是一样的。稍后我们将进一步讨论这个问题。

电晶体闸极使用替代性闸极制程制造,包括沈积牺牲层(通常为多晶矽)、图案化与蚀刻,形成大约30个较宽的条形(stripe)区域。这些条形区域可定义出电晶体闸极长度。

图3:三星Exynos7420的NMOS电晶体横截面图

(来源:TechInsights)

接着,侧壁间隔层(SWS)沿着闸极侧面形成,并且用于作为掘入蚀刻定义及随后的外延生长——为NMOS电晶体(eSi)生长矽,以及为PMOS电晶体生长矽锗(eSiGe)等。在完全形成源极/汲极后,以氧化物填充腔室,接着再进行化学机械研磨(CMP)制程。

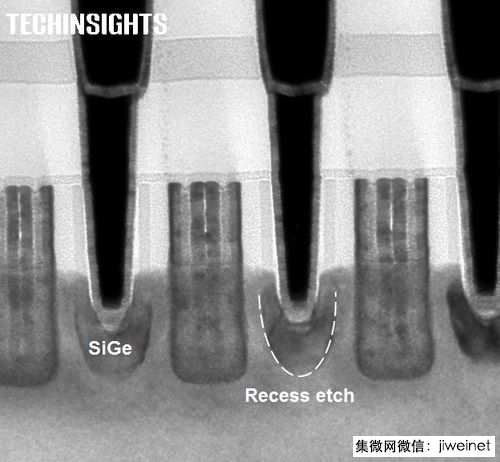

PMOS源极/汲极区域的SiGe具有围绕矽鳍的较大晶格常数,因而在PMOS电晶体上产生压缩应变,从而提高其驱动电流。大量掺杂的SiGe与NMOSeSi源极/汲极也包覆在鳍片两侧,为钨填充的触点提供较大的接触贴片,从而为电晶体实现更低的接触电阻。

图4:三星14nm节点的PMOS电晶体管

(来源:TechInsights)

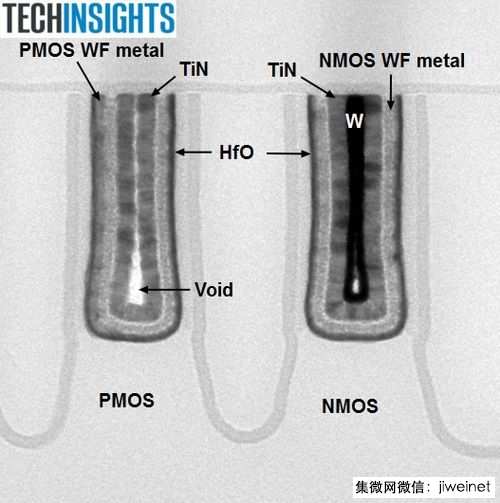

在此移除该牺牲层闸极,并以其闸电介质与金属填充该闸极。图5显示金属填充的NMOS与PMOS电晶体,两个闸极就位于隔离区域的正上方。这些电晶体共用一个通用的氧化铪(HfO)/氧化物高k闸极电介层堆叠。高密度的HfO随电晶体边缘外围绕的暗带衬托而清楚显现。闸极氧化层则环衬在HfO的表面之外。

HfO的内面则环衬着NMOS与PMOS功函数金属层,用于设定电晶体的阈值电压,这些金属分别拥有不同的组成。

闸极填充部份也有一点不同。从图中可看到NMOS电晶体的内层部份衬着氧化钛(TiN),再以钨(W)填充,但PMOS电晶体则不然。闸极长度较短的PMOS电晶体并未使用钨填充,原因在于TiN封闭闸极顶部,无法再为其填充钨;而这也导致靠近底部的部份形成真空。在闸极长度较长的PMOS电晶体由于TiN未封闭闸极顶部,因而会再度出现钨填充。

图5:虚拟NMOS和PMOS电晶体

(来源:TechInsights)

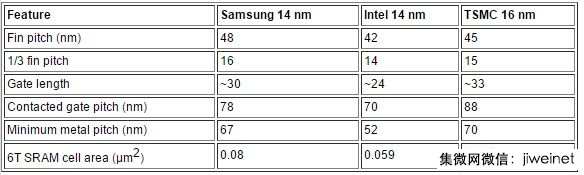

我们在前面曾经提到三星的FinFET电晶体较所描述的制程节点长度更长,但并不是只有三星如此。包括英特尔与台积电所支援的FinFET闸极长度也比其制程节点更长(如表1)。事实上,以微影尺寸的方式来看,与其所宣称的制程节点也不尽相同。这究竟是怎么一回事?

表1:三星、英特尔与台积电的电晶体尺寸比较

(来源:TechInsights)

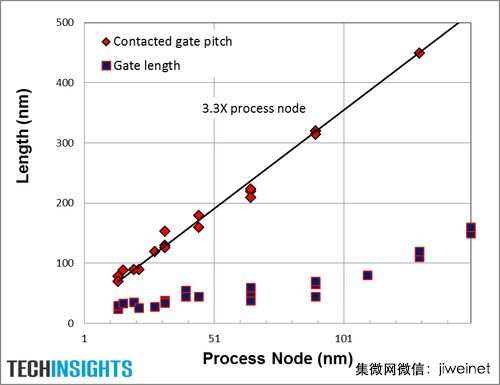

图6提供了一个线索。透过图6分别描绘出针对几个先进逻辑元件所测得的实体层闸极长度、制造商所宣称的制程节点,以及电晶体的接触闸间距。电晶体以130nm节点进行制造时,较大的闸极长度更接近制程节点。但从110nm到65nm,闸极长度微缩的速度较制程节点更快速,也比制程节点更短。至于45nm及其更小的制程,闸极长度的微缩速率则减缓。

我们还为相同的元件绘制出接触闸间距,这一间距长度是制程节点的3.3倍,而且所有的制程节点在这一点上都是一样的。我们还发现最小的金属间距也可扩展到大约3倍的制程节点。

我们经常使用接触闸间距和6TSRAM单元面积来代表制程节点;但这导致了一个问题:所谓的16nm或14nm制程节点真的是这样的节点尺寸吗?例如,三星的鳍片间距、闸极长度、接触闸间距以及6TSRAM单元面积,都比英特尔的14nm更大,其6TSRAM单元面积也比台积电的16nmSRAM更大。那么,它究竟是不是真的14nm制程?

我们之中有一名工程师认为,鳍片间距最接近于制程节点,就像我们在DRAM中看到的主动间距以及在NAND快闪记忆体中的STI间距一样。我们在表1中列出了英特尔、三星与台积电16/14nm元件的1/3鳍间距,这看起来的确更能代表制程节点。

图6:电晶体闸极长度、接触闸间距与制程节点的比较

(来源:TechInsights)

那么,我们应该可期待三星新一代的LPP制程有些什么变化?三星在最近的新闻发布中提到LPP制程将可提高15%的电晶体开关速度,同时降低15%的功耗。这些都是透过增加电晶体的鳍片高度以及增强应变工程而实现的。而我则预期还会有一点点的制程微缩,从而使其电晶体尺寸与6TSRAM单元面积更接近于英特尔的14nm制程节点。

而今,我们正满心期待尽快从Apple与三星的下一代智慧型手机中取得Exynos8SoC或Snapdragon820SoC,好让我们一窥第二代14nmLPP制程节点的变化。

编译:SusanHong