集微网消息(文/王凌锋)现如今,晶圆代工行业可分为两档,台积电一档,其他公司一档。在台积电积极发展采用EUV技术的第2代7纳米制程后,传闻5纳米制程将于2019年4月试产。台积电凭借技术与庞大资本支出所铸成的“氮气加速系统”,让其竞争对手望尘莫及。

第一代7nm让台积电正式领跑

今年上半年,纯代工领域的订单量上,台积电占了全球56%。随着AMD、苹果A13的青睐,台积电有望将优势扩大到60%。而对手三星、GF、联电、中芯国际都不到10%。台积电2018年的收入也大幅攀升,远超去年的1万亿新台币。

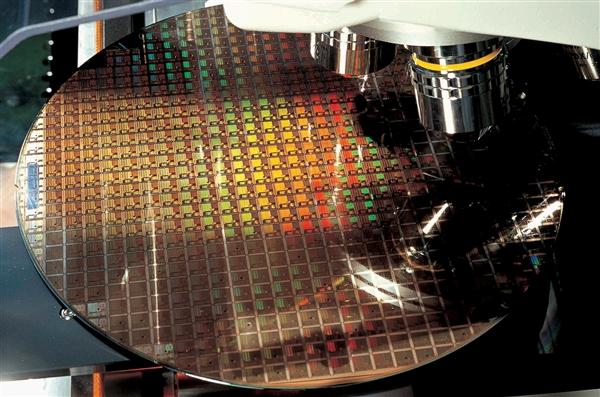

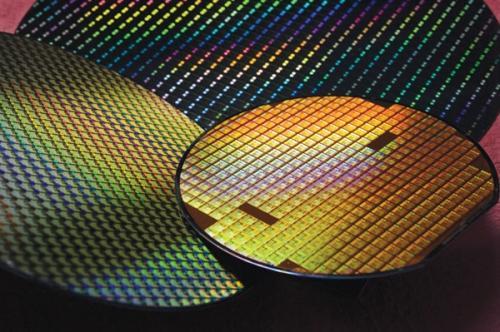

台积电最早是从2微米、3微米开始做,如今在10nm之后,最新7nm工艺也已量产出货,苹果新推出的A12仿生处理器就是由台积电独家代工制造。与之前的10nm FinFET制程相比,7nm FinFET实现1.6倍的逻辑密度,20%的速度提升,以及40%的功耗减少。在7nm技术路线的选择上,台积电务实地在第一代放弃EUV(极紫外光刻),同时上马整合扇出封装技术提升可靠度,最终使得自己的进度事实超越三星,从而赢下包括华为、AMD、苹果等一众关键客户。

EUV加持,第二代7nm又甩开老对手三星一个山头

半导体先进制程进到10纳米之下,微缩技术更加复杂,牵扯设计已经不止电路线设计,还有光刻、晶体管架构与材料等等,也让EUV极紫外光光刻成为关键技术。过去半导体生产使用波长193纳米的深紫外(DUV)曝光,但制程发展到130纳米时便有行业人士提出,需用极紫外(EUV)光刻。

EUV成为7纳米的关键技术,也是台积电、三星两大厂商技术竞逐的节点。材料供应商分析指出,导入EUV制程可以减少30个掩膜,至少能省下一个月的制程时间,进一步探讨EUV的技术脉络,为了要制造出EUV的波长电浆,必须将锡融化之后,用每秒约5万颗频率滴在真空腔体中,然后用激光以每秒10万次发射频率将液态锡蒸发成电浆,以产生EUV所需要的波长,因此激光所需要的功率以及轰击锡珠精准度,就成为EUV制程技术的“bottleneck”。

在第二代7nm工艺(CLNFF+/N7+),台积电将首次应用EUV,不过仅限四个非关键层,以降低风险、加速投产,也借此熟练掌握ASML的新式光刻机Twinscan NXE。相较于第一代7nm DUV,第二代7nm EUV具体改进程度公布得并不多,台积电只说能将晶体管密度提升20%,同等频率下功耗可降低6-12%。

面对咄咄逼人的台积电,三星也在全力以赴,正在开发自己的InFO封装技术,并宣称将在下半年量产7nm EUV。不过,在良品率和质量上,三星7nm EUV工艺仍存在风险。如今,台积电在7nm EUV工艺上成功完成流片,证明了新工艺新技术的可靠和成熟,为后续量产打下了坚实基础,同时也进一步拉开了与竞争对手三星之间的差距。

全程EUV!5nm将于明年四月风险试产

根据《EETimes》报导指出,就在台积电积极发展的第2代采用EUV技术的7纳米制程开始进行投片同时,更新一代全程采用EUV技术的5纳米制程也将于2019年的第2季进行风险试产。而且,台积电也已经与包括Cadence在内的4家合作伙伴达成协议,共同支持后段芯片设计的线上服务工作,以借由云端的服务的机制,缩短芯片设计时间,并且进一步扩大芯片设计工具的范围。

报导指出,相较于第二代使用EUV技术的7纳米制程可以处理4片掩膜来说,台积电的5纳米制程将可一次处理14片掩膜,降低生产掩膜的成本。另外,台积电还以Arm A72核心进行生产测试,5纳米制程所生产的芯片,将达到14.7%~17.7%的速度提升,以及减少1.8%~1.86%的芯片面积。号称可比初代7nm工艺晶体管密度提升80%,从而将芯片面积缩小45%,还可以同功耗频率提升15%,同频功耗降低20%。

台积电指出,虽然制程技术节点的提升,能为芯片中增加更多的晶体管,但是却也带来生产成本的大幅提升。其中,5纳米制程中包括人工与知识产权的授权费用,其加起来的总合成本将高达2到2.5亿美元,比7纳米制程的1.5亿美元大幅成长,而这也会是未来发展半导体制程,门槛越来越高的原因。

在联电与格芯相继搁置7纳米及其以下先进制程的研发之后,目前在先进制程研发的路上仅剩下台积电、三星、英特尔等少数公司。只是,英特尔在10纳米制程节点上遭遇瓶颈,预计要到2019年底才会推出的情况下,在先进制程的这条路上,也只有三星能看见台积电的尾灯了。

至此,台积电在晶圆代工行业的老大哥地位坐实,而唯一有竞争力的三星想要超车也难乎其难。

.jpg)